STCO Decoded: Making Sense of System-Level Co-Design for Today’s Challenges

By: Mohamed Arafa

From chiplets to advanced packaging to cross-domain simulation - System Technology Co-Optimization (STCO) is emerging as the engine of semiconductor progress.

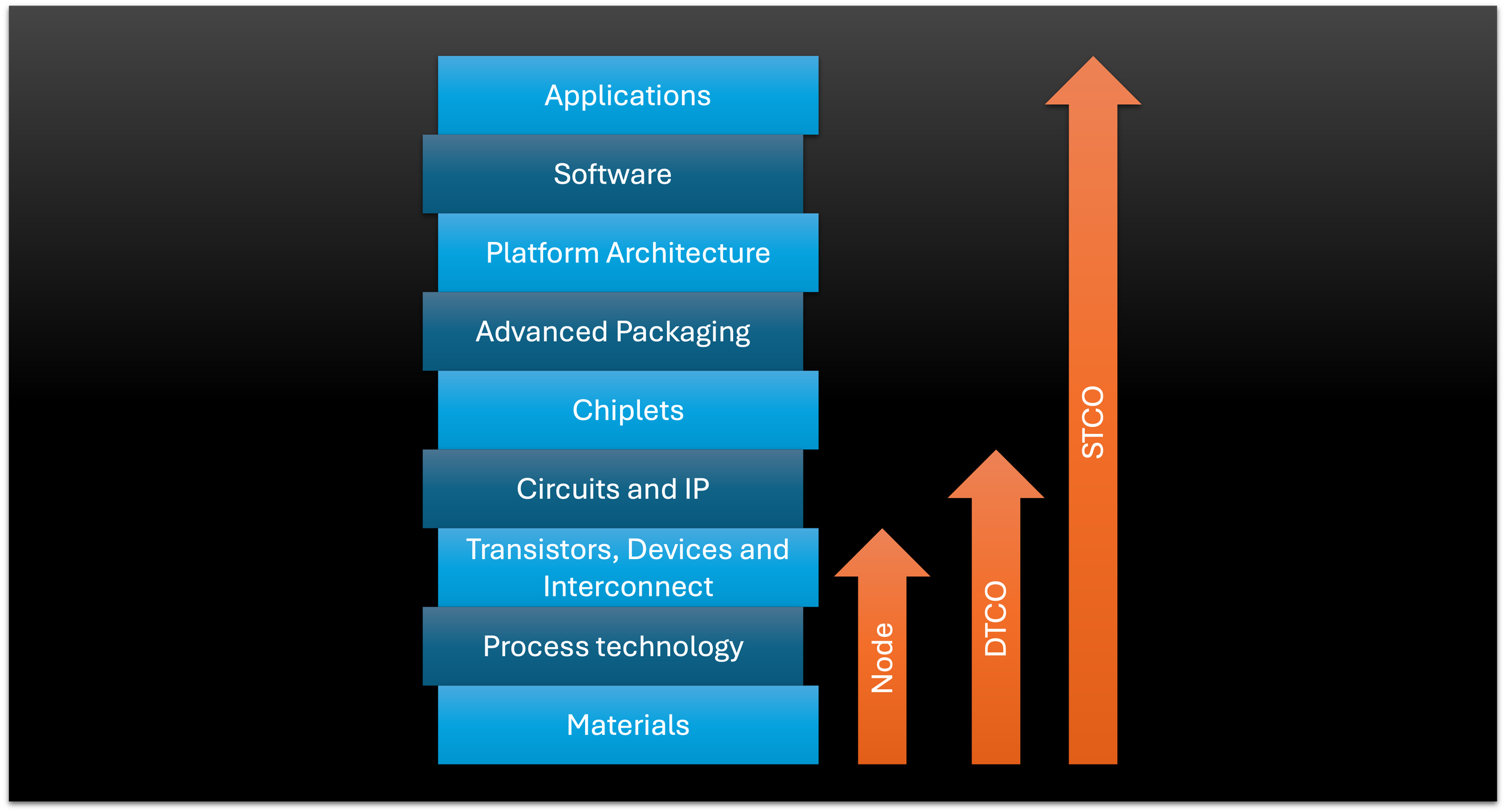

For decades, Moore’s Law and Dennard Scaling provided the semiconductor industry with a reliable roadmap for node scaling. Smaller transistors and more efficient on-chip interconnect delivered better performance and lower power opening the door for higher level of integration. However, as node scaling reaches its physical and economic limits, this approach is increasingly insufficient. Modern systems, especially those supporting AI, high-performance computing, and data-centric workloads are defined not by a single node, but by the performance of the entire compute system. Design Technology Co-Optimization (DTCO) provided a path to maintain the continuous improvement for Power, Performance, Area and Cost (PPAC)for a while. But we are now at a point where DTCO is not enough. We are at a stage where optimizing overall system performance and efficiency takes precedence over focusing solely on a specific node. STCO is a holistic methodology that optimizes technology across all layers of the system stack, ensuring that architectural, physical, and functional decisions are made collaboratively rather than in isolation.

What Is STCO?

System Technology Co-Optimization (STCO) is a system-first design methodology that aims to optimize performance, power, and cost across all layers of the compute stack—from materials and transistors to packaging and software. Unlike traditional Design-Technology Co-Optimization (DTCO), which focused on optimizing individual process nodes, STCO acknowledges the growing interdependence between layers: memory technology choices affect power delivery and thermal design, while packaging constraints influence bandwidth, signal integrity, and chiplet placement. The economic driver of Moore’s Law has weakened, with cost per transistor plateauing below the 28nm node due to process complexity and yield challenges. Simultaneously, modern workloads—such as large language models, generative AI, and edge inference—demand dramatically more memory, bandwidth, and energy efficiency. In fact, scaling limitations have already forced disaggregation of SRAM and analog circuits to older nodes, requiring sophisticated re-integration techniques within the package. This has introduced new complexities in power delivery, thermal management, and system partitioning. As workload characteristics evolve and feedback cycles lengthen, optimizing each domain in isolation is no longer viable. STCO offers a structured approach to co-develop architecture, physical integration, and technology vectors in unison—making it not only timely, but essential.

STCO Layers

Understanding the STCO Hierarchy: Layer by Layer

System Technology Co-Optimization (STCO) is best understood as a layered hierarchy where each level of abstraction, from materials to applications, influences and is influenced by the others. Below is a breakdown of the key layers in the STCO stack, each representing a critical opportunity for optimization and cross-domain collaboration:

Applications: These specify system goals such as AI inference, cloud tasks, or autonomous driving, setting limits on latency, throughput, memory, and energy use.

Software: Compilers, runtimes, and frameworks impact how efficiently applications use hardware resources. Software-hardware co-design is critical for exposing and exploiting system capabilities.

Platform Architecture: This defines how compute, memory, storage, and I/O are organized across the board-, rack-, or datacenter-levels. This goes beyond the package. It influences power delivery, thermal zoning, and physical integration of components.

Advanced Packaging: Technologies such as 2.5D interposers, and chiplet-based integration provide the physical backbone for heterogeneous systems.

Chiplets: Functions are disaggregated and re-integrated through chiplets, enabling modular design, cross-node optimization, and scalable manufacturing. Chiplets can be then organized in a 3D or 2D/2.5D manner.

Circuits and IP: Standard cells, memory macros, and interface blocks must be tailored to each chiplet’s context and process, balancing performance, power, and area constraints.

Transistors, Devices, and Interconnect: Device choices and interconnect topologies directly impact energy per bit, signal integrity, and die area. These must be aligned with system-level requirements.

Process Technology: Innovations in lithography, and etch define the limits of integration, variability, and cost. These choices should be made with system-level objectives in mind.

Materials: At the foundation, new materials for transistors, interconnects, and packaging layers enable continued performance scaling and thermal management at nanoscale dimensions.

STCO requires optimizing not just within a layer, but across layers e.g., selecting materials that support thermal constraints of 3D packaging, or adjusting circuit design based on the limitations of a particular power delivery topology. This cross-layer mindset is what enables transformative gains in PPAC (performance, power, area, cost), particularly in a post-Moore's Law world.

STCO Pilalrs

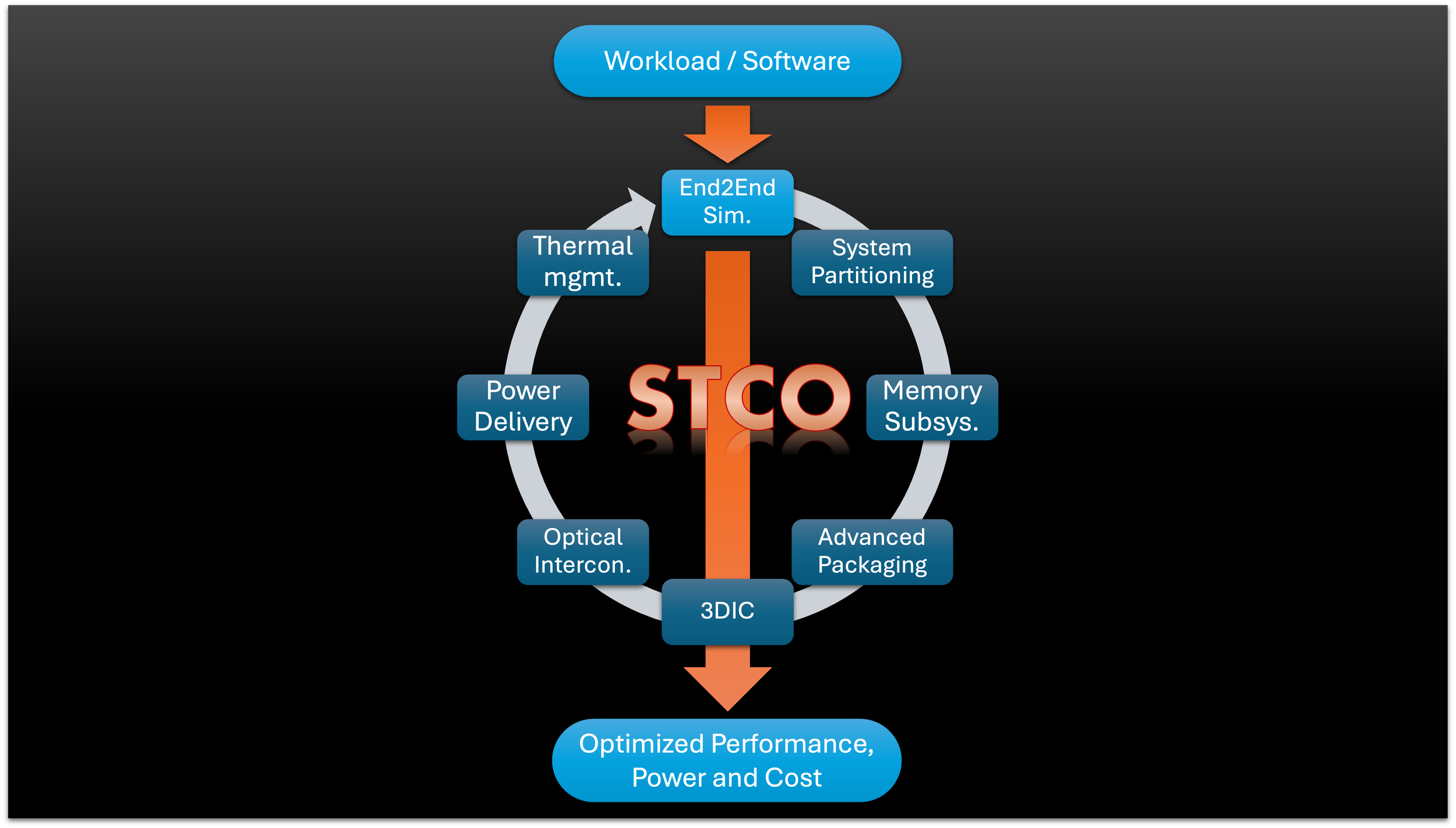

The Pillars of STCO: Where Innovation Meets Integration

To bring the STCO vision into practice, innovation must be focused across a set of technical pillars. These are critical domains where performance, power, and cost are most sensitive to design decisions. While these pillars are not the only optimization vectors available, they represent high-leverage, near-term opportunities in today’s AI-driven system designs. Other vectors—most notably software co-optimization—remain critical. Software development cycles are typically longer and feedback loops are more delayed. This blog takes a hardware-centric perspective but as the end-to-end system simulation tools continue to evolve, software-hardware co-design will become more tightly integrated into the STCO workflow.

Memory Subsystems

As AI and data-centric workloads continue to grow, memory has emerged as the dominant bottleneck in modern systems. Future systems require not just high capacity but also high bandwidth and locality. This places memory physically closer to compute through 2.5D or 3D integration. Techniques like disaggregated SRAM chiplets, processing-in-memory, and hybrid-bonded DRAM can unlock performance- and energy-efficiency, but demand careful trade-offs in cost, coherence, and thermals. Memory architecture is now a system-defining choice, not just a module-level parameter.

Power Delivery Networks (PDNs)

Delivering hundreds of amps at sub-volt levels through advanced packages and stacked die is one of the greatest challenges in modern electronics. STCO calls for, integrated voltage regulation, power-aware partitioning, package-level current distribution and co-optimization of backside Power Delivery Networks (PDNs) where applicable. Emerging materials such as GaN and SiC, as well as embedded capacitors, offer new levers to improve efficiency. At the same time, every choice must consider thermal coupling, noise isolation, and mechanical integrity.

Advanced Packaging

The package is no longer a passive container. It is now a performance-critical substrate that must support dense interconnects, complex routing, thermal extraction, and multi-chiplet integration. Technologies like 2.5D interposers, fan-out RDL, and glass substrates enable tighter integration, while wafer-scale packaging pushes the limits of monolithic-like performance. Packaging decisions today affect not only power and signal integrity, but also yield, bandwidth, reliability, and form factor.

Thermal Management

As power densities rise, especially in 3DICs, thermal becomes a gating factor. STCO elevates thermal from a constraint to a design variable, requiring thermally aware chiplet placement, innovative Thermal Interface Materials (TIM), embedded cooling structures, and system-level airflow or liquid cooling. Thermal isolation is just as important as conductivity; protecting sensitive analog or memory elements from high-power digital tiles is essential for reliability and precision.

3D Integrated Circuits (3DICs)

3D integration offers a revolutionary step forward in memory bandwidth, latency reduction, and area efficiency. Fine-pitch hybrid bonding, TSVs, and wafer-to-wafer stacking all play a role in building dense vertical systems. However, 3DICs also introduce new challenges in mechanical stress, yield, heat removal, and power delivery. STCO ensures that 3D integration is used where it brings net system value, not just as a feature checkbox.

Optical Interconnects

To scale beyond copper, optical interconnects provide low-latency, high-bandwidth data movement that is largely independent of distance. Co-packaged optics (CPO) and wafer-level photonics are making their way into data center and HPC platforms, offering reduced power-per-bit and thermal decoupling. Integrating optics into a system demands cross-pillar collaboration spanning packaging, materials, signal integrity, and system layout.

System Partitioning and Chiplet Integration

Disaggregating large monolithic dies into chiplets offers benefits in yield, modularity, and process-node optimization. But once disaggregated, reintegration must be precise: each chiplet interface brings latency, power, and area overhead. STCO enables smart partitioning strategies that account for manufacturing feasibility, interconnect pitch, packaging limitations, and functional locality while trying to minimize cost.

End-to-End System Simulation

To guide STCO decisions across all these pillars, simulation must move beyond point tools into integrated, AI-accelerated environments. This includes fast-turnaround, cross-domain simulators that account for workload variability, telemetry standards for tool interoperability, and machine-learning models that can generalize across design spaces. Agentic AI and digital twins further enhance exploration and traceability, turning simulation into a strategic asset for system design. These advances are also critical to accelerating software-hardware co-design, reducing development time and improving feedback fidelity across the stack.

How SemiTech Insights Enables STCO

SemiTech Insights is a consulting partner committed to helping organizations embrace and apply STCO principles in real-world environments. Our offerings map directly to the key STCO pillars:

Strategy and Technical Analysis: We provide technical insight to benchmarking across memory, interconnect, packaging, and chip partitioning domains.

Business Development and Commercialization: We help transform early-stage R&D into differentiated, manufacturable technologies with clear ROI.

Proposal and Program Development: We assist in aligning technical roadmaps with funding initiatives, including CHIPS Act opportunities.

Independent Technical Evaluation: We perform neutral reviews of packaging, memory architecture, power delivery, and more to de-risk your system strategy.

Roadmaps, Reports, and Publications: We distill state-of-the-art STCO research into actionable insights that inform product planning and competitive positioning.

Workforce Development: We design training programs to upskill engineers in various aspects of the architecture, circuits and semiconductor technology.

Vision Beyond the Package

While many STCO activities begin at the package-level, the full vision extends beyond the package into boards, racks, and entire platforms. Power delivery, cooling, signal integrity, and system interconnects must all be evaluated together. Platform architecture, including system disaggregation, optical interconnect adoption, and data center layout, all influence whether innovations at the silicon level will deliver real-world benefits. SemiTech Insights bridges the gap between silicon-centric innovation and platform-level gains.

Final Thoughts

System Technology Co-Optimization (STCO) is far more than a buzzword. It's a practical response to the limitations of traditional scaling and the rising complexity of modern compute systems. STCO provides a unified framework for the compute system to be optimized in an integrated design space. STCO ensures that breakthroughs in memory, packaging, chiplets, and system integration translate into scalable, system-level performance. In future blogs, we will dive deeper into the specific pillars of STCO highlighting emerging technologies and techniques to maintain the needed cadence for innovation.